Digital - Frontend & Backend

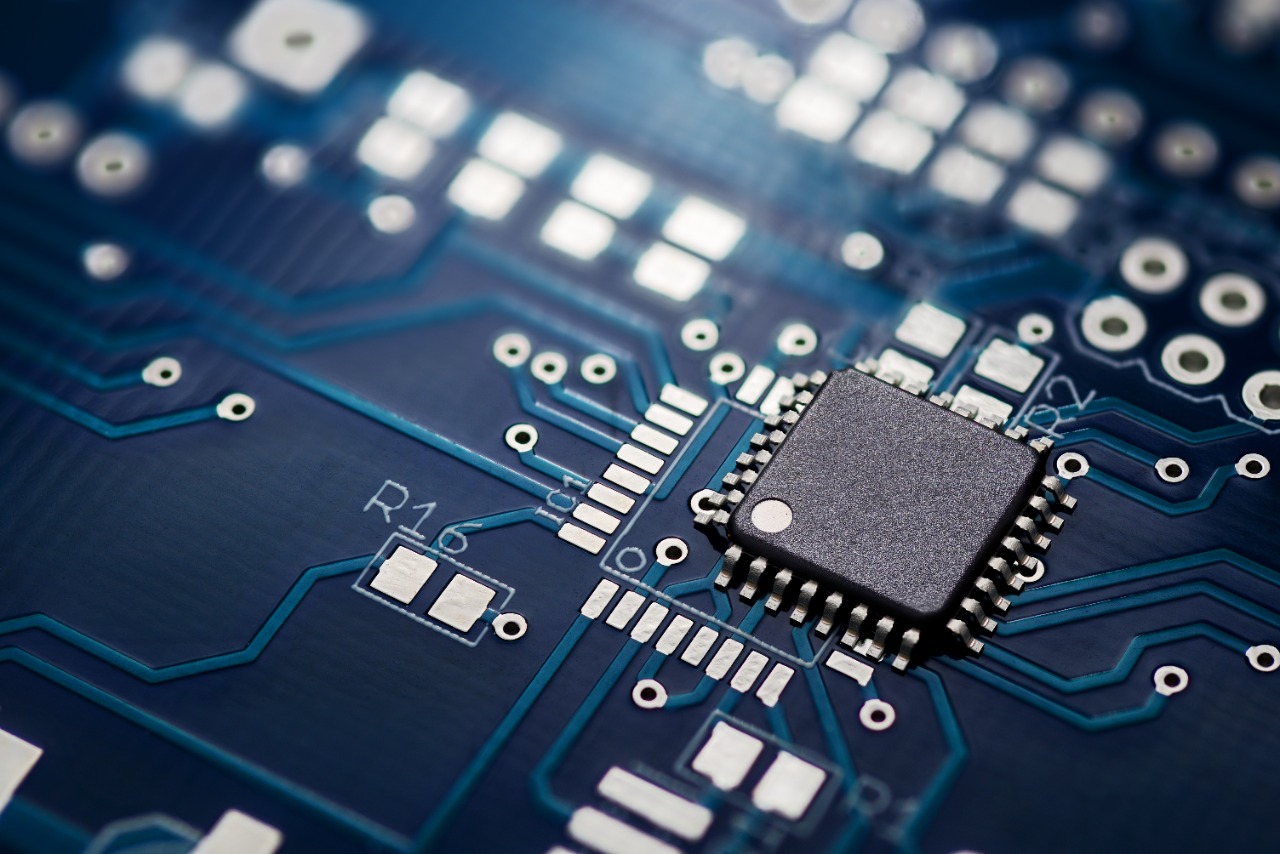

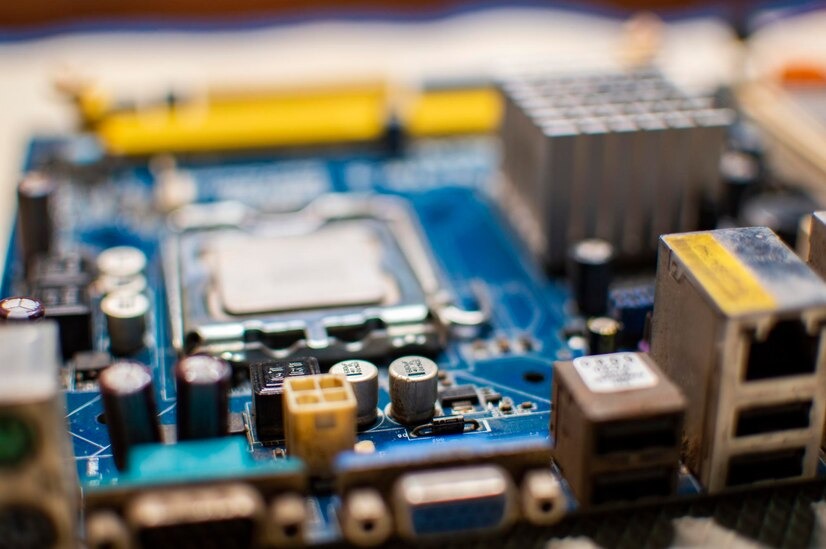

Design Specification to Netlist and Netlist to GDSII for ASIC Development

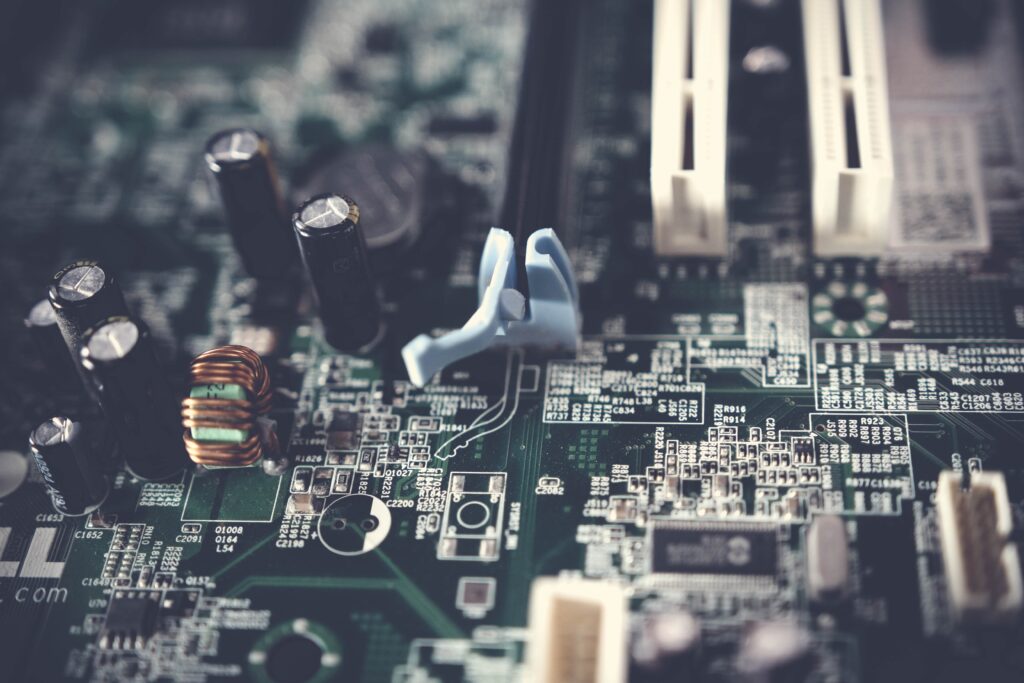

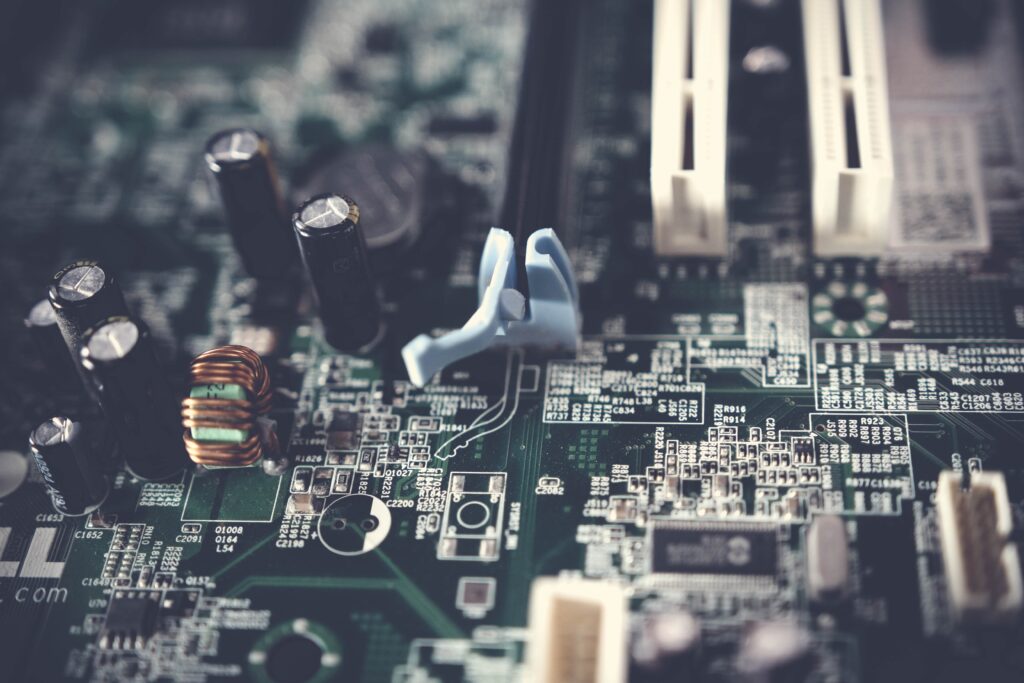

Analog, Mixed Signal & Technology Foundation

Circuit, Layout & Char for AMS, IOs, Memories, and Std Cell Libs

Tincidunt feugiat dapibus dictum imperdiet eu auctor ligula facilisis platea. Faucibus elit rhoncus dolor quis eget senectus. Facilisi velit donec morbi dolor nostra eros. Dignissim nostra dapibus morbi fames enim montes ante.

Design Specification to Netlist and Netlist to GDSII for ASIC Development

Circuit, Layout & Char for AMS, IOs, Memories, and Std Cell Libs

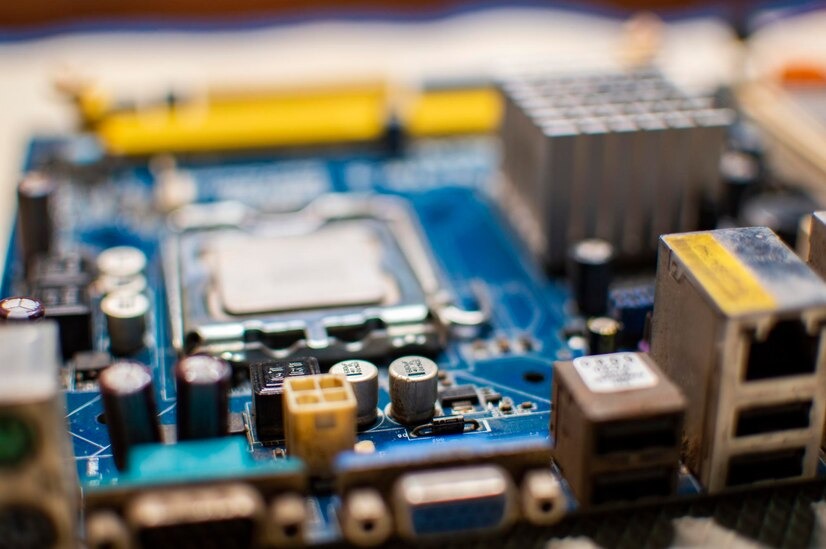

Microarchitecture , RTL Design ,

RTL Signoff , Synthesis

DFT, P&R, CTS, STA, PV, Low Power implementation

Circuit, Layout & Characterization for

AMS, RF, IOs,

Memories & Std Cell Libs

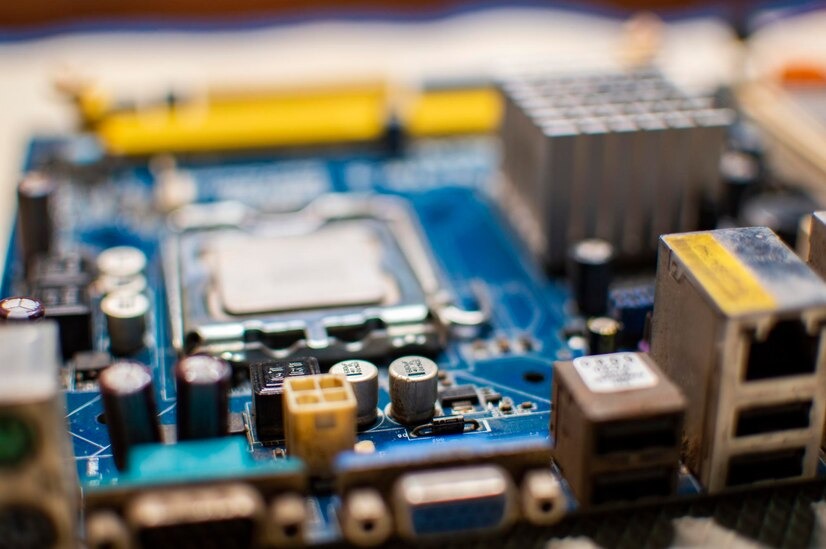

Embedded Firmware Dev

Board Bring-Up, and Validation

Automation using SHELL, TCL, PERL

PYTHON, SKILL & more

Microarchitecture , RTL Design ,

RTL Sign off , Synthesis

DFT, P&R, CTS, STA, PV instead of PNR,

STA Low Power implementation

Circuit, Layout & Characterization for

AMS, RF, IOs,

Memories & Std Cell Libs

Embedded Firmware Dev

Board Bring-Up, and Validation

Automation using SHELL, TCL, PERL

PYTHON, SKILL & more

We provide Embedded software/firmware development and porting services for Industrial Automation, Smart home automation, Computer Vision, Remote sensor networks.

"The Engineers from Frenustech played a big role during tape out of Signalchip's SoC. They were not only dedicated towards work but always ready to put in something extra each day. They had a keen sense to learn about any new block assigned to them and were always up to challenges of the physical design of complicated blocks. The Engineers were also involved during the parasitic back annotation of complex RF blocks and tried to understand the problems being faced by the Designers and came up with innovative layout architectures to address the issues."

We have been working with FrenusTech for the past 5 years and can confidently say that they are the best in terms of commitment and quality of deliverables. They have been a constant support at all times with their team often working late nights and during the weekends as well, during project releases. Ramesh and his team have always ensured that sufficient resources are always available if any situation arises because of change in project delivery timelines. It is always a pleasure to work with his team and hope for continued collaboration in the future.

Copyright © 2024 Kysos-Semi, Powered by Insideout