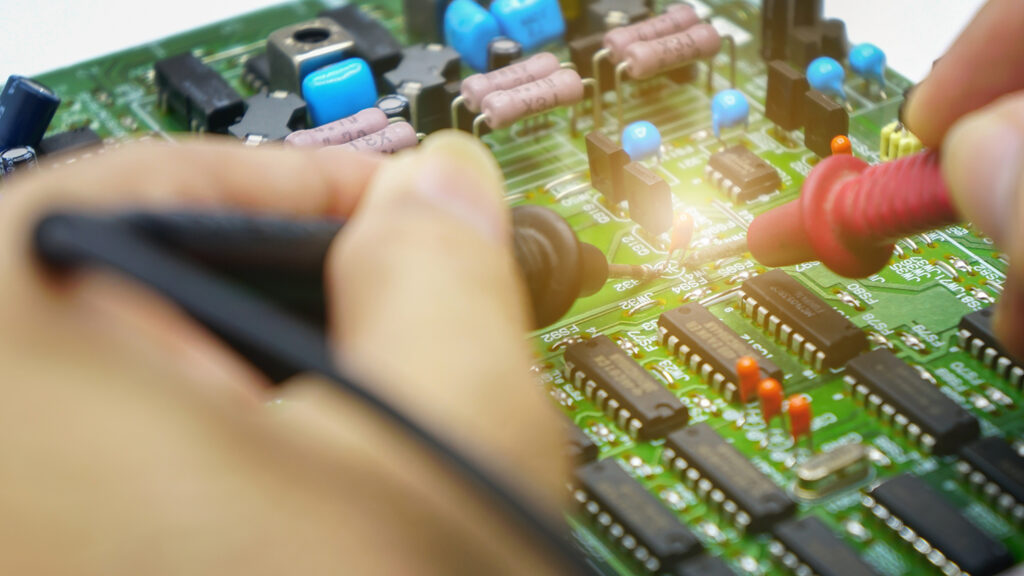

Physical Design

- Block/SoC level full ownership of RTL to GDSII

- Analog Block Integration

- Low Power Methodology

- Synthesis

- STA

- Floorplanning

- Placement and Routing

- Power Planning / Optimization

- Clock Tree Synthesis

- Cross-talk / Thermal / Noise Analysis

- IR drop and Signal Integrity Closure

- Physical Verification (DRC, LVS, ERC, Customer-specific Checks)

- ICC2, Innovus, Caliber, RC, DC, RedHawk, PT / PTSI

- TCL, SHELL, Perl & Python Scripting

- 5nm & Lower Nodes | UMC, TSMC, Intel, GF & more

- Logical Equivalence Check